Verilog 语言编写一个 半加器 电路模块

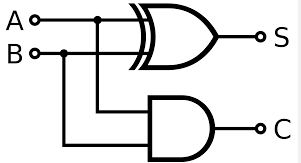

半加器 的电路结构:

S = A 异或 B C = A 与 B

1. 程序代码

module h_adder (A, B, SO, CO); input A, B; output SO, CO; assign SO = A ^ B; assign CO = A & B;endmodule

2. 解释程序代码

- 关键词

module与endmodule就像一个括号({}),任何一个功能模块的描述都必须放在此 “括号” 里面。 h_adder是模块的名字,名字自定义。h_adder后面的括号和括号里的内容叫做:外部端口表。括号里面的内容:A, B, SO, CO,就是这个模块中所有 外部端口 ,外部端口的名字自定义,类似 C语言 函数的形参。如果将这段程序比喻成一个电路的话,那么外部端口就是这个电路中引出的引脚。- 使用

input和output等关键字来定义 外部端口(A, B, SO, CO)的属性。input和output等关键字叫做:端口关键词。如果 外部端口 是输出引脚,就定义为:output;如果 外部端口 是输入引脚,就定义为:input;如果 外部端口 是输入输出引脚,就定义为:inout。 - 以关键字

assign引导的语句,是描述这个模块(当前例子的模块名为:h_adder)的逻辑功能和电路结构。简单的说,实现功能的语句使用关键字assign来修饰。

这样的一个模块程序,就相当于一个具有某种功能的电路模块硬件。比如:上面这段代码的功能就是 半加器 这个电路的功能。

3. 程序代码中需要注意的几点

- 模块的名字(

h_adder),在命名的时候,需要注意:名称不能使用数字开头;不能出现中文;不能与EDA软件库中已定义好的关键词或元件名相同,比如:or2、latch等。 - 除了

endmodule语句不需要,其他的每条语句都使用 分号(;) 做为结束。 - 定义外部端口时,端口关键词(

input、output、inout等)后面可以定义多个外部端口,端口名之间使用逗号(,)相隔,最后加上 分号(;)。

4. 程序模板

模块语句的一般格式如下:

module 模块名 外部端口表 ; 定义外部端口属性 模块的功能描述endmodule

参考:

《EDA技术实用教程 — Verilog HDL版(第五版)》 3.1节 P59